## **Data Device Corporation**

#### SCS3740 Rad Hard SBC and Next Gen SBC using the GR740

Robert Hillman, Engineering Director, DDC Space

December 15th, 2022 GR740 User day

### Overview

**Component and SBC Roadmaps**

Volatile and Non-Volatile memory applicable to GR740/GR765

Existing SCS3740 using the GR740

Fully qualified, shipping flight boards now

**GR740 Technical challenges**

SCS3740G2 (RT and RH)

In Development, with engineering boards Q3/2023

FM SBC's available in Q4/2024

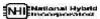

## DDC Space Business Unit Memory Component Roadmap

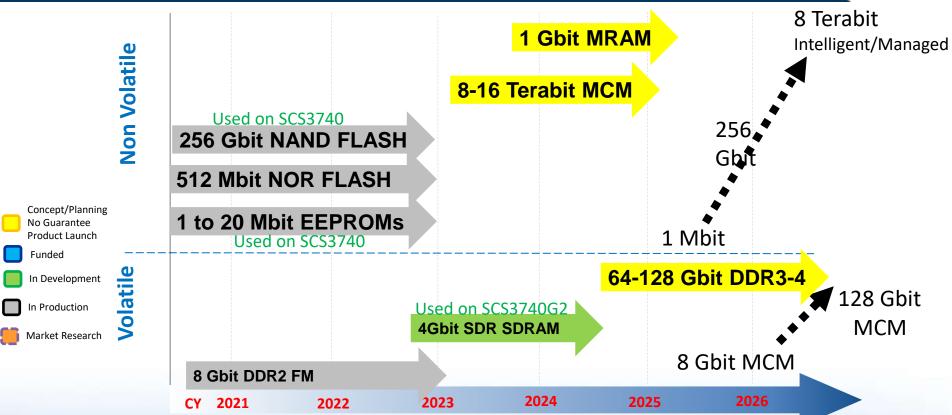

## Space Business Unit Board Product Roadmap

## New 84SD12832 – 4Gbit SDR SDRAM MCM

#### 4Gbit SDR (Single Data Rate) SDRAM

- Up to 100MHz Single Data rate SDRAM

- 16 or 32 bit wide data bus, ceramic/hermetic package

- Excellent package signal integrity/power integrity

- Makes board level design easier and improve Worst case analysis

- Compatible with many processors/FPGA's

- DDC is using these SDRAM's on the SCS3740 and next gen SCS3740G2

- 3.3V I/O for FPGA, GR740 processor compatibility

- Future: Other densities/bus widths contact DDC

1.2" x 0.9" package For existing 72SD3232 (1Gbit) And for new 84SD12832 (4Gbit)

#### **Radiation Tolerance**

- >100krad (bare die before package shielding)

- SEL >80.6 MeV·cm2/mg @ 85C

- Rare SEFI's were easily cleared with MRS (mode register set)

#### **Availability:**

| Engineering | Q4-2023 |

|-------------|---------|

| Flight      | Q4-2024 |

## **New DDR2 MCM**

#### Up to 8Gbit DDR2 SDRAM

- Ceramic/Hermetic Solution (CCGA Package)

- Up to 800M Data rate SDRAM

- Bus widths of 8, 16, 32, 40, 48, 64 and 80

- Excellent package signal integrity/power integrity

- Makes board level design easier and improve Worst case analysis

- Compatible with many processors/FPGA's

- DDC is working on WCA/app note for RTG4 FPGA

- Future: DDR3/DDR4 contact DDC

0.985" x 0.630" package For all densities/bus widths

#### **Radiation Tolerance**

>100krad (bare die before package shielding)

SEL >85.6 MeV·cm2/mg @ 125C

Much better SEU/SEFI rates than DDR3 and DDR4 products (Rad report available upon request)

#### **Availability**:

Engineering NOW

Flight NOW

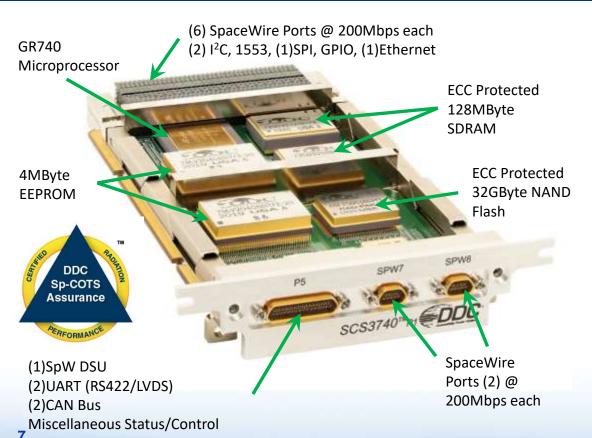

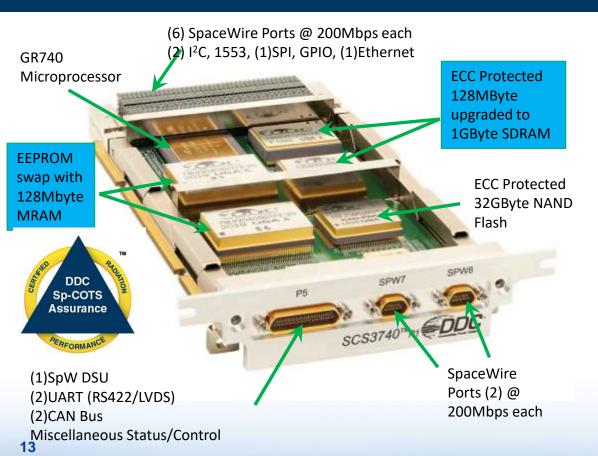

## 3U Rad Hard Space VPX SCS3740

- GR740: Quad-Core LEON 4FT™

- 1700 Dhrystone MIPS

- 128MB ECC SDRAM

- 32GB ECC Flash

- 4MB EEPROM

- 1553\* (Requires external PHY)

- Debug via Ethernet, JTAG or SpW

- Weight: 550g

- Fully Qualified and shipping flight

**Low Power - 5W typical, 3.3V only**

## **SCS3740 – Radiation Tolerance**

- 100 krad(Si) TID for entire SBC (orbit dependent)

- Uncorrectable upset rate better than 1 in 120 years (GEO)

- Existing and next gen SCS3740G2 will both have industry leading upset rates

- GR740 LEON 4FT™ Processor

- STMicro C65SPACE RHBD Library 300Krad(Si), SEL immune

- Architecture implements combination of RHBD FFs, TMR, Parity and ECC

- Memory ECC:

- Reed Solomon SDRAM error correction (multi-nibble correction)

- NAND Flash advanced BCH correction (16 bit correction)

- Rad Hard Microchip RTAX FPGA

- Rad Hard POL, Clocks, etc.

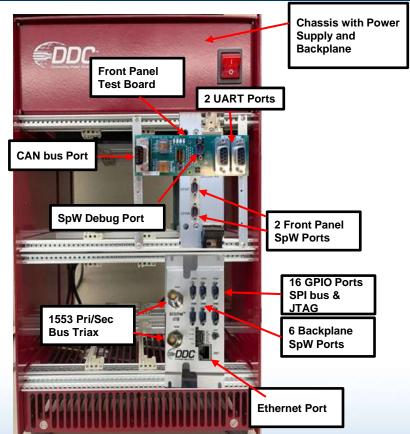

# SCS3740 & SCS3740DK6-CBUF Software Development Kit

User Test Board (UTB)

## Technical Challenges – GR740

- GR740 – Ethernet timing (125Mhz) – unable to support GbE

| Name                  | Parameter                         | Reference edge           | Min | Max  | Unit |

|-----------------------|-----------------------------------|--------------------------|-----|------|------|

| t <sub>ETH0GMII</sub> | transmitter clock to output delay | rising (GMII) clock edge | 1.5 | 10.5 | ns   |

GR740 to SDRAM timing – unable to support 100MHz even with 2T Signaling

| Name                | Parameter                  | Reference edge            | Min | Max  | Unit |

|---------------------|----------------------------|---------------------------|-----|------|------|

| t <sub>SDRAM0</sub> | clock to output delay      | rising mem_clk_in<br>edge | 2.5 | 12.0 | ns   |

| <sup>t</sup> SDRAM1 | clock to data output delay | rising mem_clk_in<br>edge | 2.5 | 12.0 | ns   |

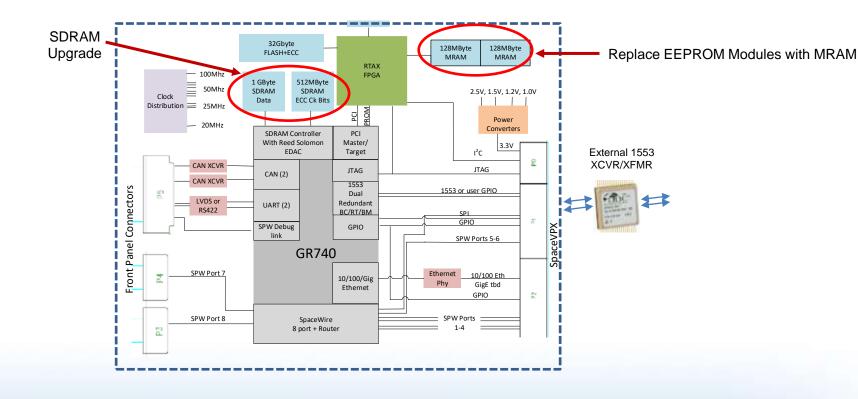

## DDC's GR740 2<sup>nd</sup> Gen SBC - SCS3740G2

SCS3740G2 pinout and functionally compatible with Existing SCS3740 Increased SDRAM from 128MByte to 1GByte Increased boot memory (non FLASH)

- SCS3740 currently is 4MByte EEPROM

- SCS3740G2 increased to 128MByte MRAM

- Includes redundant SuROM and OS images

- VxWorks 7 and Linux support (planned Q4 2023)

Higher Performance FLASH Memory

Adding BCH Error Correction in hardware

SBC available in low cost RT (30krad) as well as RH (100krad)

## SCS3740G2 (In Development)

## 3U Space VPX SCS3740G2

- Main changes:

- Upgraded boot memory to 128Mbyte

- Upgraded SDRAM to 1GByte

- Increased flash file system speed

- New ordering options

- RT lower cost option: 30krad

- RH for 100krad

- Operating System Options:

- VxWorks 7.0 (baseline)

- Linux (planned)

- Easy upgrade from existing 3740R1

- Same pinout/interfaces/arch.

- 3740R1 available now

- 3740G2 dev boards avail Q3-2023

Blue boxes designate SCS3740G2 changes from existing SCS3740R1 SBC